آی سی رم Ram IC 46v32m16-6t

240.000 تومان

آی سی رم IC Ram 46v32m16-6t

دانلود دیتاشیت در انتهای همین صفحه . . .

ویژگی ها 46v32m16-6t

VDD + 2.5 ولت 0.2 ولت، VDDQ + 2.5 ولت ± 0.2 ولت بارق داده دو طرفه (DQS) ارسال/دریافت با داده، به عنوان مثال، ضبط داده همزمان با منبع (x16 دارای دو عدد یک در هر بایت) داخلی، خط لوله با سرعت داده دوگانه معماری (DDR)؛

توضیحات

آی سی رم IC Ram 46v32m16-6t

ویژگی ها

VDD + 2.5 ولت ± 0.2 ولت، VDDQ + 2.5 ولت ± 0.2 ولت بارق داده دو طرفه (DQS) ارسال/دریافت شده با داده، به عنوان مثال، ضبط داده همزمان با منبع (x16 دارای دو ¬ یک در هر بایت) داخلی، داده دوطرفه خط لوله معماری نرخ (DDR)؛ دو دسترسی به داده در هر چرخه ساعت ورودی های ساعت دیفرانسیل (CK و CK#)

دستورات وارد شده در هر لبه مثبت CK DQS هم تراز با داده ها برای READ. تراز مرکزی با دادهها برای WRITEs DLL برای تراز کردن انتقالهای DQ و DQS با CK چهار بانک داخلی برای عملیات همزمان ماسک داده (DM) برای پوشاندن دادههای نوشتن (x16 دارای دو ¬یک در هر بایت) طولهای پشت سر هم قابل برنامهریزی:آی سی رم IC Ram 46v32m16-6t

یا 8 حالت بازخوانی خودکار و بازخوانی خودکار TSOP سرب طولانیتر برای قابلیت اطمینان بهبود یافته (OCPL) 2.5 ولت ورودی/خروجی (سازگار با SSTL_2) گزینه پیششارژ خودکار همزمان پشتیبانی میشود قفل tRAS پشتیبانی میشود (tRAP = tRCD)

گزینه ها

آی سی رم IC Ram 46v32m16-6t

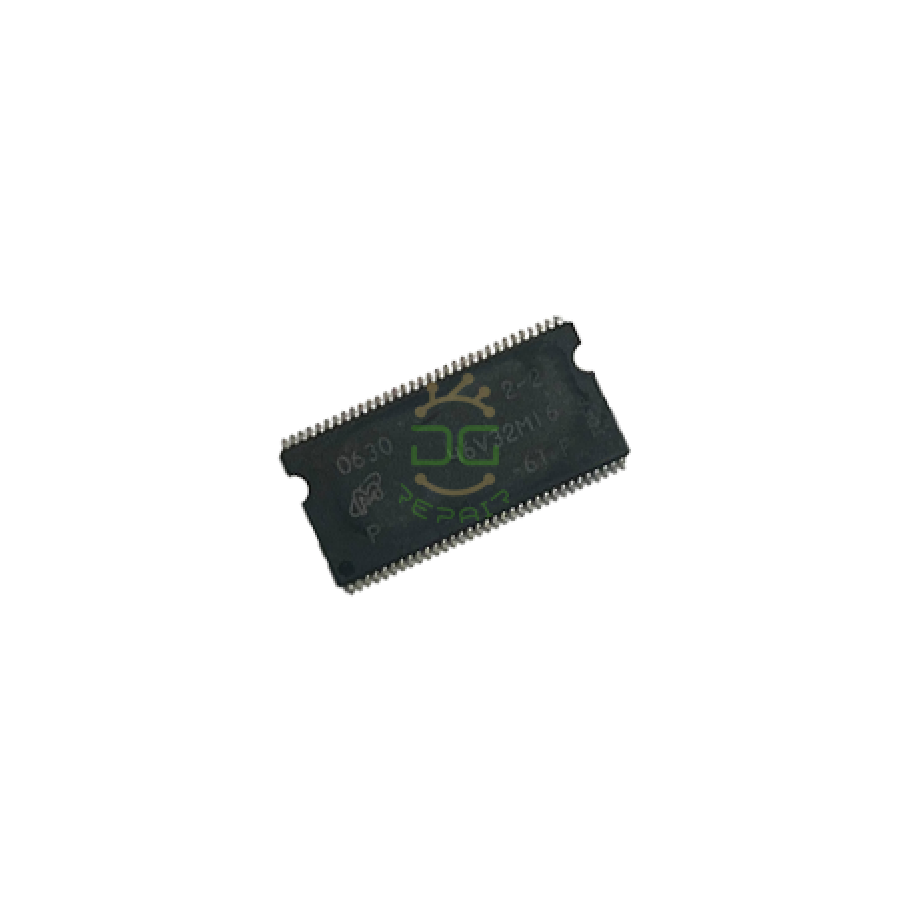

پیکربندی 128 مگ 4 (بانک های 32 مگ) 64 مگ 8 (بانک های 16 مگ) 32 مگ 16 (8 مگ 4 بانک) بسته پلاستیکی TSOP 66 پین (عرض 400 میلی متر، گام پین 0.65 میلی متر) TSOP میل 66 پین (400) عرض، گام پین 0.65 میلی متر) FBGA 60 توپ بدون سرب (10×12.5 میلی متر) 60 توپ FBGA (10×12.5 میلی متر) زمان بندی بدون سرب ¬ زمان چرخه 2.5 (DDR333)1 (فقط FBGA) 2.5)1 (DDR33) فقط TSOP) 2.5 (DDR266B) 4،5 خود نوسازی استاندارد درجه حرارت کم توان خود به روز رسانی درجه حرارت استاندارد صنعتی تا +85 درجه سانتی گراد)

پیکربندی بازخوانی تعداد ردیف آدرسدهی بانک آدرسدهی ستون آدرسدهی

درجه سرعت CL=2 CL=2.5 DATA-OUT WINDOW7 ACCESS WINDOW DQS¬DQ SKEW

پشتیبانی از ماژول های PC2700 با زمان بندی 2.5-3-3 پشتیبانی از ماژول های PC2100 با زمان بندی 2-2-2 پشتیبانی از ماژول های PC2100 با زمان بندی 2-3-3 پشتیبانی از ماژول های PC2100 با زمان بندی 2.5-3-3 پشتیبانی از ماژول های PC1600 با زمان بندی 2-2-2 CL = CAS (خواندن) تاخیر حداقل نرخ ساعت (-75E، -75Z) و CL= 2.5 (-6T،-75)

و مشخصات مورد بحث در اینجا فقط برای ارزیابی و مقاصد مرجع است و در معرض تغییر میکرون بدون اطلاع قبلی است. محصولات فقط توسط MICRON برای مطابقت با مشخصات برگه داده تولید MICRON ضمانت می شوند.

شماره قطعه مثال: MT46V32M16TG-75Z MT46V تنظیمات بسته سرعت گزینههای دمای ویژه

تنظیمات دمای عملیاتی 128 Meg x4 64 Meg x8 32 Meg 32M16 L Package 400 mil TSOP 400 mil TSOP Lead-free x 12.5mm FBGA x 12.5mm FBGA Lead-free -75Z -75 Low Speed Industrial Grade = Industrial Special Option

512 مگابایت DDR SDRAM یک حافظه پرسرعت CMOS و با دسترسی تصادفی پویا و حاوی 536870912 بیت است. این به صورت داخلی به عنوان یک DRAM چهار بانکی پیکربندی شده است.

SDRAM DDR 512 مگابایتی از معماری سرعت داده دوگانه برای دستیابی به عملکرد با سرعت بالا استفاده می کند. معماری سرعت داده دوگانه اساساً یک معماری 2nprefetch با رابطی است که برای انتقال دو کلمه داده در هر چرخه ساعت در پین های I/O طراحی شده است. یک دسترسی خواندن یا نوشتن واحد برای SDRAM 512 مگابایتی DDR به طور موثر شامل یک انتقال داده با پهنای 2n بیت

و یک چرخه ساعت در هسته DRAM داخلی و دو انتقال داده متناظر با پهنای n بیت و چرخه نیم ساعتی در پین های ورودی/خروجی یک بارق داده دو طرفه (DQS) به صورت خارجی همراه با داده ها برای استفاده در ضبط داده در گیرنده منتقل می شود.

آی سی رم IC Ram 46v32m16-6t

DQS یک strobe است که توسط DDR SDRAM در حین خواندن و توسط کنترل کننده حافظه در هنگام WRITE ارسال می شود.

DQS با داده ها برای READ ها تراز لبه و برای WRITE ها با داده ها تراز وسط است. ارائه x16 دارای دو استروب داده است، یکی برای بایت پایین و دیگری برای بایت بالا. 512 مگابایت DDR SDRAM از یک ساعت دیفرانسیل (CK و CK#) کار می کند.

عبور از CK با رفتن به HIGH و CK# با رفتن به LOW به عنوان لبه مثبت CK نامیده می شود. دستورات (آدرس و سیگنال های کنترل) در هر لبه مثبت CK ثبت می شوند. داده های ورودی

در هر دو لبه DQS ثبت می شود و داده های خروجی به هر دو لبه DQS و همچنین به هر دو لبه CK ارجاع می شود.

دسترسی های خواندن و نوشتن به DDR SDRAM به صورت انفجاری است. دسترسی ها از یک مکان انتخاب شده شروع می شوند و برای تعداد برنامه ریزی شده مکان ها در یک دنباله برنامه ریزی شده ادامه می یابند. دسترسی ها با ثبت یک فرمان ACTIVE شروع می شود که سپس با یک دستور READ یا WRITE دنبال می شود.

آی سی رم IC Ram 46v32m16-6t

بیت های آدرس ثبت شده همزمان با دستور ACTIVE برای انتخاب بانک و ردیف مورد نظر استفاده می شود. بیت های آدرس ثبت شده همزمان با دستور READ یا WRITE برای انتخاب بانک و محل ستون شروع برای دسترسی انفجاری استفاده می شود. DDR SDRAM طول های پشت سر هم READ یا WRITE قابل برنامه ریزی یا 8 مکان را فراهم می کند. یک عملکرد پیششارژ خودکار ممکن است فعال شود تا یک پیششارژ ردیف خود زمانبندیشده ارائه کند که در پایان یک انفجار پشت سر هم آغاز میشود.

Features

آی سی رم IC Ram 46v32m16-6t

VDD +2.5V ±0.2V, VDDQ +2.5V ±0.2V Bidirectional data strobe (DQS) transmitted/ received with data, i.e., source-synchronous data capture (x16 has two one per byte) Internal, pipelined

double-data-rate (DDR) architecture; two data accesses per clock cycle Differential clock inputs

آی سی رم IC Ram 46v32m16-6t

(CK and CK#) Commands entered on each positive CK edge DQS edge-aligned with data for READs; centeraligned with data for WRITEs DLL to align DQ and DQS transitions with CK Four internal banks for concurrent operation Data mask (DM) for masking write data (x16 has two one per byte) Programmable burst lengths: or 8 Auto Refresh and Self Refresh Modes Longer lead TSOP for improved reliability (OCPL) 2.5V I/O (SSTL_2 compatible) Concurrent auto precharge option is supported tRAS lockout supported (tRAP = tRCD)

آی سی رم IC Ram 46v32m16-6t

x8 x16 VDD NF DQ0 VDDQ DQ1 DQ2 VSSQ VssQ DQ2 DQ4 VDDQ DQ3 DQ6 VSSQ VssQ DQ7 NC VDDQ NC LDQS NC VDD DNU NC LDM WE# CAS# RAS# CS# A2 A3 VDD

x16 VSS DQ15 VSSQ DQ14 DQ13 VDDQ DQ12 DQ11 VSSQ DQ10 DQ9 VDDQ DQ8 NC VSSQ UDQS DNU VREF VSS UDM CK# CK CKE A5 A4 VSS

x8 VSS DQ7 VSSQ NC DQ6 VDDQ NC DQ5 VSSQ NC DQ4 VDDQ NC VSSQ DQS DNU VREF VSS DM CK# CK CKE A5 A4 VSS

x4 VSS NF VSSQ NC DQ3 VDDQ NC NF VSSQ NC DQ2 VDDQ NC VSSQ DQS DNU VREF VSS DM CK# CK CKE A5 A4 VSS

OPTIONS

Configuration 128 Meg 4 (32 Meg banks) 64 Meg 8 (16 Meg banks) 32 Meg 16 (8 Meg x 4 banks) Plastic Package 66-pin TSOP(400 mil width, 0.65mm pin pitch) 66-pin TSOP(400 mil width, 0.65mm pin pitch) Lead-Free 60-Ball FBGA (10×12.5mm) 60-Ball FBGA (10×12.5mm) Lead-Free Timing Cycle Time 2.5 (DDR333)1 (FBGA only) 2.5 (DDR333)1 (TSOP only) 2.5 (DDR266B)4,5 Self Refresh Standard Low Power Self Refresh Temperature Rating Standard Industrial Temperature to +85°C)

Configuration Refresh Count Row Addressing Bank Addressing Column Addressing

آی سی رم IC Ram 46v32m16-6t

SPEED GRADE CL=2 CL=2.5 DATA-OUT WINDOW7 ACCESS WINDOW DQSDQ SKEW

Supports PC2700 modules with 2.5-3-3 timing Supports PC2100 modules with 2-2-2 timing Supports PC2100 modules with 2-3-3 timing Supports PC2100 modules with 2.5-3-3 timing Supports PC1600 modules with 2-2-2 timing CL = CAS (Read) Latency Minimum clock rate (-75E, -75Z) and CL= 2.5 (-6T,-75)

AND SPECIFICATIONS DISCUSSED HEREIN ARE FOR EVALUATION AND REFERENCE PURPOSES ONLY AND ARE SUBJECT TO CHANGE BY MICRON WITHOUT NOTICE. PRODUCTS ARE ONLY WARRANTED BY MICRON TO MEET MICRON’S PRODUCTION DATA SHEET SPECIFICATIONS.

آی سی رم IC Ram 46v32m16-6t

Example Part Number: MT46V32M16TG-75Z MT46V Configuration Package Speed Special Temperature Options

Operating Temp Configuration 128 Meg x4 64 Meg x8 32 Meg 32M16 L Package 400 mil TSOP 400 mil TSOP Lead-Free x 12.5mm FBGA x 12.5mm FBGA Lead-Free -75Z -75 Speed Grade = 2.5 Special Options Low Power IT Standard Industrial Temp

The 512Mb DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 536,870,912 bits. It is internally configured as a quadbank DRAM. The 512Mb DDR SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2nprefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the 512Mb DDR SDRAM effectively consists of a single 2n-bit wide, one-clock-cycle data transfer at the internal DRAM core and two corresponding n-bit wide, one-halfclock-cycle data transfers at the I/O pins.

A bidirectional data strobe (DQS) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the DDR SDRAM during READs and by the memory controller during WRITEs. DQS is edge-aligned with data for READs and center-aligned with data for WRITEs. The x16 offering has two data strobes, one for the lower byte and one for the upper byte. The 512Mb DDR SDRAM operates from a differential clock (CK and CK#);

the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Commands (address and control signals) are registered at every positive edge of CK. Input data

آی سی رم IC Ram 46v32m16-6t

is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK. Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command.

آی سی رم IC Ram 46v32m16-6t

The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed. The address bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access. The DDR SDRAM provides for programmable READ or WRITE burst lengths or 8 locations. An auto precharge function may be enabled to provide a selftimed row precharge that is initiated at the end of the burst access. As with standard SDR SDRAMs, the pipelined, multibank architecture of DDR SDRAMs allows for concurrent operation, thereby providing high effective bandwidth by hiding row precharge and activation time.

آی سی رم IC Ram 46v32m16-6t

An auto refresh mode is provided, along with a power-saving power-down mode. All inputs are compatible with the JEDEC Standard for SSTL_2. All full drive option outputs are SSTL_2, Class II compatible.

آی سی رم IC Ram 46v32m16-6t

NOTE: 1. The functionality and the timing specifications discussed in this data sheet are for the DLL-enabled mode of operation. 2. Throughout the data sheet, the various figures and text refer to DQs as “DQ.” The DQ term to be interpreted as any and all DQ collectively, unless specifically stated otherwise.

Additionally, the x16 is divided into two bytes, the lower byte and upper byte. For the lower byte (DQ0 through DQ7) DM refers to LDM and DQS refers to LDQS. For the upper byte (DQ8 through DQ15) DM refers to UDM and DQS refers to UDQS. 3. Complete functionality is described throughout the document and any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements. 4. Any specific requirement takes precedence over a general statement.

Micron Technology, Inc., reserves the right to change products or specifications without notice. ©2003 Micron Technology, Inc. All rights reserved.

آی سی رم IC Ram 46v32m16-6t

Features.1 512Mb DDR SDRAM Part Numbers.2 General Description.2 Functional Description.12 Initialization.12 Register Definition.12 Mode Register.12 Burst Length.13 Burst Type.13 Read Latency.14 Operating Mode.14 Extended Mode Register.15 Output Drive Strength.15 DLL DESELECT.17 NO OPERATION (NOP).17 LOAD MODE WRITE.17 PRECHARGE.17 Auto Precharge.17 BURST TERMINATE.18 AUTO REFRESH.18 SELF REFRESH.18 Operations.19 Bank/Row WRITEs.29 PRECHARGE.40 Power-down (CKE Not Active).40 Absolute Maximum Ratings.46 Notes.57 Data Sheet Designation.77

نقد و بررسیها

هنوز بررسیای ثبت نشده است.